Режимы передачи данных

IEEE 1284 определяет пять режимов обмена, один из которых полностью соответствует стандартному выводу по протоколу Centronics. Стандарт определяет способ, по которому ПО может определить режим, доступный и хосту (PC), и ПУ (или присоединенному второму компьютеру). Режимы нестандартных портов, реализующих протокол обмена Centronics аппаратно (Fast Centronics, Parallel Port FIFO Mode), могут и не являться режимами IEEE 1284, несмотря на наличие в них черт ЕРР и ЕСР.

При описании режимов обмена фигурируют следующие понятия:

-

- Хост -

компьютер, обладающий параллельным портом.

- ПУ - периферийное устройство, подключаемое к этому порту.

- Ptr - в обозначениях сигналов обозначает передающее ПУ.

- Прямой канал - канал вывода данных от хоста в ПУ.

- Обратный канал - канал ввода данных в хост из ПУ.

Полубайтный режим ввода - Nibble Mode

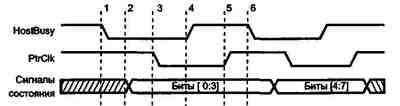

Предназначен для двунаправленного обмена. Может работать на всех стандартных портах. Порты имеют 5 линий ввода состояния, используя которые ПУ может посылать в хост байт тетрадами (nibble - полубайт, 4 бита) за два приема. Сигнал Ack#, вызывающий прерывание, которое может использоваться в данном режиме, соответствует биту 6 регистра состояния, что усложняет программные манипуляции с битами при сборке байта. Сигналы порта приведены в табл. 4, временные диаграммы - на рис. 3.

Рис. 3. Прием данных в полубайтном режиме

Прием байта данных в полубайтном режиме состоит из следующих фаз:

- Хост сигнализирует о готовности приема данных установкой низкого уровня на линии HostBusy.

- ПУ в ответ помещает тетраду на входные линии состояния.

- ПУ сигнализирует о готовности тетрады установкой низкого уровня на линии PtrClk.

- Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой тетрады.

- ПУ отвечает установкой высокого уровня на линии PtrClk.

- Шаги 1-5 повторяются для второй тетрады.

Таб.

4. Сигналы порта

|

Контакт

|

Сигнал

SPP

|

I/O

|

Описание

|

|

14

|

AutoFeed#

|

0

|

HostBusy

- сигнал квитирования. Низкий уровень означает готовность к приему

тетрады, высокий подтверждает прием тетрады

|

|

17

|

Sdectln#

|

0

|

Высокий

уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень

низкий)

|

|

10

|

Ack#

|

1

|

PtrClk.

Низкий уровень означает готовность тетрады, высокий - ответ на сигнал

HostBusy

|

|

11

|

Busy

|

I

|

Прием

бита данных 3, затем бита 7

|

|

12

|

РЕ

|

I

|

Прием

бита данных 2, затем бита 6

|

|

13

|

Sdect

|

I

|

Прием

бита данных 1, затем бита 5

|

|

15

|

Error"

|

I

|

Прием

бита данных 0, затем бита 4

|

Полубайтный режим сильно нагружает процессор, и поднять скорость обмена выше 50 Кбайт/с не удается. Безусловное его преимущество в том, что он работает на всех портах. Его применяют в тех случаях, когда поток данных невелик (например, для связи с принтерами). Однако при связи с адаптерами локальных сетей, внешними дисковыми накопителями и CD-ROM прием больших объемов данных требует изрядного терпения со стороны пользователя.Двунаправленный байтный режим - Byte Mode

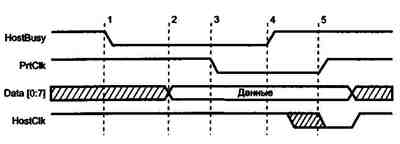

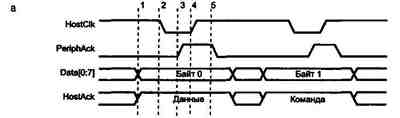

В данном режиме данные принимаются с использованием двунаправленного порта, у которого выходной буфер данных может отключаться установкой бита СR.5=1. Как и предыдущие, режим является программно-управляемым - все сигналы квитирования анализируются и устанавливаются драйвером. Сигналы порта описаны в табл. 5, временные диаграммы - на рис. 4.

Таб.

5. Сигналы порта

|

Контакт

|

Сигнал

SPP

|

Имя

в байтном режиме

|

I/O

|

Описание

|

|

*

|

Strobe"

|

HostClk

|

0

|

Импульс (низкого уровня) подтверждает прием байта в конце каждого цикла |

|

14

|

AutoFeed#

|

HostBusy

|

0

|

Сигнал квитирования. Низкий уровень означает готовность хоста принять байт; высокий уровень устанавливается по приему байта |

|

17

|

Selecting

|

1284Active

|

0

|

Высокий уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий) |

|

16

|

lnit#

|

lnit

|

0

|

Не используется; установлен высокий уровень |

|

10

|

Ack#

|

PtrClk

|

I

|

Устанавливается в низкий уровень для индикации действительности данных на линиях Data [0:7]. Низкий уровень устанавливается в ответ на сигнал HostBusy |

|

11

|

Busy

|

PtrBusy

|

I

|

Состояние занятости прямого канала |

|

12

|

PE

|

AckDataReq*

|

1

|

Устанавливается ПУ для указания на наличие обратного канала передачи |

|

13

|

Select

|

Xflag*

|

I

|

Флаг расширяемости |

|

15

|

Error#

|

DataAvail#*

|

I

|

Устанавливается ПУ для указания на наличие обратного канала передачи |

|

2-9

|

Data

[0:7]

|

Data

[0:7]

|

I/0

|

Двунаправленный (прямой и обратный) канал данных |

* Сигналы действуют в последовательности согласования (см. далее).

Рис. 4. Прием данных в байтном режиме

Фазы приема байта данных:

- Хост сигнализирует о готовности приема данных установкой низкого уровня на линии HostBusy.

- ПУ в ответ помещает байт данных на линии Data [0:7].

- ПУ сигнализирует о действительности байта установкой низкого уровня на линии PtrClk.

- Хост устанавливает высокий уровень на линии HostBusy, указывая на занятость приемом и обработкой байта.

- ПУ отвечает установкой высокого уровня на линии PtrClk.

- Хост подтверждает прием байта импульсом HostCIR.

- Шаги 1-6 повторяются для каждого следующего байта.

Побайтный режим позволяет поднять скорость обратного канала до скорости прямого канала в стандартном режиме. Однако он может работать только на двунаправленных портах.

Режим ЕРР

Протокол ЕРР (Enhanced Parallel Port - улучшенный параллельный порт) был разработан компаниями Intel, Xircom и Zenith Data Systems задолго до принятия IEEE 1284. Он предназначен для повышения производительности обмена по параллельному порту. ЕРР был реализован в чипсете Intel 386SL (микросхема 82360) и впоследствии принят множеством компаний как дополнительный протокол параллельного порта. Версии протокола, реализованные до принятия IEEE 1284, отличаются от нынешнего стандарта (см. далее).

Протокол ЕРР обеспечивает четыре типа циклов обмена:

- запись данных;

- чтение данных;

- запись адреса;

- чтение адреса.

Назначение циклов записи и чтения данных очевидно. Адресные циклы используются для передачи адресной, канальной и управляющей информации. Циклы обмена данными отличаются от адресных циклов применяемыми стробирующими сигналами. Назначение сигналов порта ЕРР и их связь с сигналами SPP объясняются в табл. 6.

Таб. 6. Назначение сигналов порта ЕРР и их связь с сигналами SPP

|

Контакт

|

Сигнал

SPP

|

Имя

в ЕРР

|

I/O

|

Описание

|

|

1

|

Strobe

|

Write#

|

0

|

Низкий уровень - цикл записи, высокий - цикл чтения |

|

14

|

AutoLF#

|

DataStb#

|

0

|

Строб

данных. Низкий уровень устанавливается в циклах передачи данных |

|

17

|

Selecting

|

AddrStbft

|

0

|

Строб адреса. Низкий уровень устанавливается в адресных циклах |

|

16

|

lnit

|

Reset

|

0

|

Сброс ПУ (низким уровнем) |

|

10

|

Ack#

|

INTR#

|

I

|

Прерывание от ПУ |

|

11

|

Busy

|

Wait#

|

Сигнал квитирования. Низкий уровень разрешает начало цикла (установку строба в низкий уровень), переход в высокий - разрешает завершение цикла (снятие строба) | |

|

2-9

|

Data

[0:7]

|

AD[0:7]

|

I/O

|

Двунаправленная шина адреса/данных |

|

12

|

PaperEnd

|

AckDataReq*

|

I

|

Используется по усмотрению разработчика периферии |

|

13

|

Select

|

Xflag*

|

I

|

Используется по усмотрению разработчика периферии |

|

15

|

Error#

|

DataAvail#*

|

I

|

Используется по усмотрению разработчика периферии |

* Сигналы действуют в последовательности согласования (см. далее). 2 Зак.╧530

ЕРР-порт имеет расширенный набор регистров (табл. 7), который занимает в пространстве ввода/вывода 5-8 смежных байт.

Таб.

7.

EPP-порт

|

Имя

регистра

|

Смещение

|

Режим

|

R/W

|

Описание

|

|

SPP

Data Port

|

+0

|

SPP/EPP

|

W

|

Регистр данных SPP |

|

SPP

Status Port

|

+1

|

SPP/EPP

|

R

|

Регистр состояния SPP |

|

SPP

Control Port

|

+2

|

SPP/EPP

|

W

|

Регистр управления SPP |

|

EPP

Address

Port |

+3

|

EPP

|

R/W

|

Регистр адреса EPP. Чтение или запись в него генерирует связанный цикл чтения или записи адреса EPP |

|

EPP

Data Port

|

+4

|

EPP

|

R/W

|

Регистр данных EPP. Чтение (запись) генерирует связанный цикл чтения (записи) данных EPP |

|

Not

Defined

|

+5...+7

|

EPP

|

N/A

|

В некоторых контроллерах могут использоваться для 16-/32-битных операций ввода/вывода |

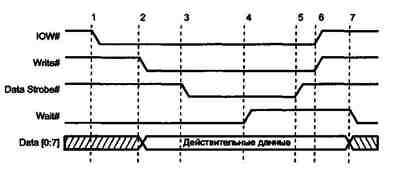

В отличие от программно-управляемых режимов, описанных ранее, внешние сигналы fPP-порта для каждого цикла обмена формируются аппаратно по одной операции записи или чтения в регистр порта. На рис. 1.5 приведена диаграмма цикла записи данных, иллюстрирующая внешний цикл обмена, вложенный в цикл записи системной шины процессора (иногда эти циклы называют связанными). Адресный цикл записи отличается от цикла данных только стробом внешнего интерфейса.

Цикл записи данных состоит из следующих фаз:

- Программа выполняет цикл вывода (IOWR#) в порт 4 (EPP Data Port).

- Адаптер устанавливает сигнал Write* (низкий уровень), и данные помещаются на выходную шину LPT-порта.

- При низком уровне Wart# устанавливается строб данных.

- Порт ждет подтверждения от ПУ (перевода Wait# в высокий уровень).

- Снимается строб данных - внешний ЕРР-цикл завершается.

- Завершается процессорный цикл вывода.

- ПУ устанавливает низкий уровень Wait#, указывая на возможность начала следующего цикла.

Рис. 5. Цикл записи данных ЕРР

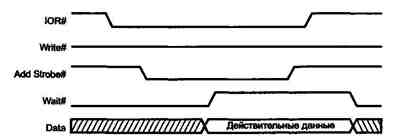

Пример адресного цикла чтения приведен на рис. 6. Цикл чтения данных отличается только применением другого стробирующего сигнала.

Рис. 6. Адресный цикл чтения ЕРР

Главной

отличительной чертой ЕРР является выполнение внешней передачи во время

одного процессорного цикла ввода/вывода. Это позволяет достигать высоких

скоростей обмена (0,5...2 Мбайт/с). ПУ, подключенное к параллельному порту

ЕРР, может работать со скоростью устройства, подключаемого через слот

ISA. Протокол блокированного квитирования (interlocked handshakes) позволяет

автоматически настраиваться на скорость обмена, доступную и хосту, и ПУ.

ПУ может регулировать длительность всех фаз обмена

с помощью всего лишь одного сигнала Wait#. Протокол автоматически подстраивается

под длину кабеля - вносимые задержки приведут только к удлинению цикла.

Поскольку кабели, соответствующие IEEE 1284 (см. выше), имеют одинаковые

волновые свойства для разных линий, нарушения передачи, связанного с "состязаниями"

сигналов, происходить не должно. При подключении сетевых адаптеров или

внешних дисков к ёPP-nopTy можно наблюдать непривычное явление: снижение

производительности по мере удлинения интерфейсного кабеля.

Естественно, ПУ не должно "подвешивать" процессор на шинном цикле обмена. Это гарантирует механизм тайм-аутов PC, который принудительно завершает любой цикл обмена, длящийся более 15 мкс. В ряде реализации ЕРР за тайм-аутом интерфейса следит сам адаптер - если ПУ не отвечает в течение определенного времени (5 мкс), цикл прекращается и в дополнительном (не стандартизованном) регистре состояния адаптера фиксируется ошибка.

Устройства

с интерфейсом ЕРР, разработанные до принятия IEEE 1284, отличаются началом

цикла: строб DataStb# или AddrStb# устанавливается независимо от состояния

WAIT#. Это означает, что ПУ не может задержать начало следующего цикла

(хотя может растянуть его на требуемое время). Такая спецификация называется

ЕРР 1.7 (предложена Xircom). Именно она применялась в контроллере 82360.

Периферия, совместимая с ЕРР 17, будет нормально работать

и с контроллером ЕРР 1284, но периферия в стандарте ЕРР 1284 может отказаться

работать с контроллером ЕРР 1.7. С

программной точки зрения контроллер ЯРР-порта выглядит просто (см. табл.

7). К трем регистрам стандартного порта, имеющим смещение 0, 1 и 2 относительно

базового адреса

порта, добавлены два регистра (ЕРР Address Port и ЕРР Data Port), чтение

и запись в которые вызывает генерацию связанных внешних циклов.

Назначение регистров стандартного порта сохранено для совместимости fPP-порта с ПУ и ПО, рассчитанными на применение программно-управляемого обмена. Поскольку сигналы квитирования адаптером вырабатываются аппаратно, при записи в регистр управления СП биты 0, 1 и 3, соответствующие сигналам Strobeft, AutoFeed# и Selecting должны иметь нулевые значения. Программное вмешательство могло бы нарушить последовательность квитирования. Некоторые адаптеры имеют специальные средства защиты (ЕРР Protect), при включении которых программная модификация этих бит блокируется. Использование регистра данных ЕРР позволяет осуществлять передачу блока данных с помощью одной инструкции REP INSB или REP OUTSB. Некоторые адаптеры допускают 16-/32-битное обращение к регистру данных ЕРР. При этом адаптер просто дешифрует адрес со смещением в диапазоне 4-7 как адрес регистра данных ЕРР, но процессору сообщает о разрядности 8 бит. Тогда 16- или 32-битное обращение по адресу регистра данных ЕРР приведет к автоматической генерации двух или четырех шинных циклов по нарастающим адресам, начиная со смещения 4. Эти циклы будут выполняться быстрее, чем то же количество одиночных циклов. Таким образом обеспечивается производительность до 2 Мбайт/с, достаточная для адаптеров локальных сетей, внешних дисков, стриммеров и CD-ROM. Адресные циклы ЕРР всегда выполняются только в однобайтном режиме.

Важной чертой ЕРР является то, что обращение процессора к ПУ осуществляется в реальном времени - нет буферизации. Драйвер способен отслеживать состояние и подавать команды в точно известные моменты времени. Циклы чтения и записи могут чередоваться в произвольном порядке или идти блоками. Такой тип обмена удобен для регистроориентированных ПУ или ПУ, работающих в реальном времени, - сетевых адаптеров, устройств сбора информации и управления и т. п.

Режим ЕСР

Протокол ЕСР (Extended Capability Port - порт с расширенными возможностями) был предложен Hewlett Packard и Microsoft для связи с ПУ типа принтеров или сканеров. Как и ЕРР, данный протокол обеспечивает высокопроизво дительный двунаправленный обмен данными хоста с ПУ.

Протокол ЕСР в обоих направлениях обеспечивает два типа циклов:

- циклы записи и чтения данных;

- командные циклы записи и чтения.

Командные циклы подразделяются на два типа: передачу канальных адресов и передачу счетчика RLC (Run-Length Count).

В отличие от ЕРР, вместе с протоколом ЕСР сразу появился стандарт на программную (регистровую) модель его адаптера, изложенный в документе "The IEEE 1284 Extended Capabilities Port Protocol and ISA Interface Standard" компании Microsoft. Этот документ определяет свойства протокола, не заданные стандартом IEEE 1284:

- компрессию данных хост-адаптером по методу RLE;

- буферизацию FIFO для прямого и обратного каналов;

- применение DMA и программного ввода/вывода.

Компрессия в реальном времени по методу RLE (Run-Length Encoding) позволяет достичь коэффициента сжатия 64:1 при передаче растровых изображений, которые имеют длинные строки повторяющихся байт. Компрессию можно использовать, только если ее поддерживает и хост, и ПУ.

Канальная адресация ЕСР применяется для адресации множества логических устройств, входящих в одно физическое. Например, в комбинированном устройстве факс/принтер/модем, подключаемом только к одному параллельному порту, возможен одновременный прием факса и печать на принтере. В режиме SPP, если принтер установит сигнал занятости, канал будет занят данными, пока принтер их не примет. В режиме ЕСР программный драйвер просто адресуется к другому логическому каналу того же порта.

Протокол ЕСР переопределяет сигналы SPP (табл. 1.8).

Таб.

8. Протокол ECP

|

Контакт

|

Сигнал

SPP

|

Имя

в ЕСР

|

I/O

|

Описание

|

|

1

|

Strobe"

|

HostClk

|

0

|

Используется в паре с PeriphAck для передачи в прямом направлении (вывод) |

|

14

|

AutoLF#

|

HostAck

|

о

|

Указывает тип цикла (команда/данные) при передаче в прямом направлении. Используется в паре с PeriphClk для передачи в обратном на правлении |

|

17

|

Selecting

|

1284Active

|

о

|

Высокий уровень указывает на обмен в режиме IEEE 1284 (в режиме SPP уровень низкий) |

|

16

|

lnit#

|

ReverseRequest*

|

о

|

Низкий уровень переключает канал на передачу в обратном направлении |

|

10

|

Ack#

|

PeriphQk

|

1

|

Используется в паре с HostAck для передачи в обратном направлении |

|

11

|

Busy

|

PeriphAck

|

I

|

Используется

в паре с HostClk для передачи в обратном направлении. Индицирует тип команда/данные при передаче в обратном направлении |

|

12

|

PaperEnd

|

AckReverse#

|

I

|

Переводится в низкий уровень как подтверждение сигналу ReverseRequest# |

|

13

|

Select

|

Xflag*

|

I

|

Флаг расширяемости |

|

15

|

Error#

|

PeriphRequest#*

|

I

|

Устанавливается

ПУ для указания на доступность (наличие) обратного ка- нала передачи* |

|

2-9

|

Data

[0:7]

|

Data

[0:7]

|

I/O

|

Двунаправленный канал данных |

* Сигналы действуют в последовательности согласования (см. далее).

Адаптер ЕСР тоже генерирует внешние протокольные сигналы квитирования аппаратно, но его работа существенно отличается от режима ЕРР.

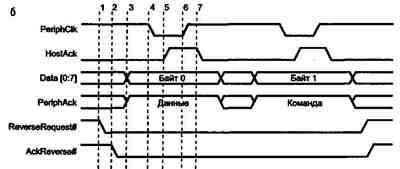

На рис. 7а приведена диаграмма двух циклов прямой передачи: за циклом данных следует командный цикл. Тип цлкла задается уровнем на линии HostAck: в цикле данных - высокий, в командном цикле - низкий. В командном цикле байт может содержать канальный адрес или счетчик RLE. Отличительным признаком является бит 7 (старший): если он нулевой, то биты 0-6 содержат счетчик RLE (0-127), если единичный - то канальный адрес. На рис. 1.76 показана пара циклов обратной передачи.

|

|

Рис. 7. Передача в режиме ЕСР: a - прямая, б - обратная

В отличие от диаграмм обмена ЕРР, на рис. 1.7 не приведены сигналы циклов системной шины процессора. В данном режиме обмен программы с ПУ разбивается на два относительно независимых процесса, которые связаны через FIFO - буфер. Обмен драйвера с FIFO-буфером может осуществляться с использованием как DMA, так и программного ввода-вывода. Обмен ПУ с буфером аппаратно выполняет адаптер ЕСР. Драйвер в режиме ЕСР не имеет информации о точном состоянии процесса обмена, но здесь обычно важно только то, завершен он или нет. Прямая передача данных на внешнем интерфейсе состоит из следующих шагов:

Хост помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии HostAck.

- Хост устанавливает низкий уровень на линии HostClk, указывая на действительность данных.

- ПУ отвечает установкой высокого уровня на линии PeriphAck.

- Хост устанавливает высокий уровень линии HostClk, и этот перепад может использоваться для фиксации данных в ПУ.

- ПУ устанавливает низкий уровень на линии PeriphAck для указания на готовность к приему следующего байта.

Поскольку передача в ЕСР происходит через FIFO-буферы, которые могут присутствовать на обеих сторонах интерфейса, важно понимать, на каком этапе данные можно считать переданными. Данные считаются переданными на шаге 4, когда линия HostClk переходит в высокий уровень. В этот момент модифицируются счетчики переданных и принятых байт. В протоколе ЕСР есть условия, вызывающие прекращение обмена между шагами 3 и 4. Тогда эти данные не должны рассматриваться как переданные.

Из

рис. 7 видно и другое отличие ЕСР от ЕРР. Протокол ЕРР позволяет драйверу

чередовать циклы прямой и обратной передачи, не запрашивая подтверждения

на смену направления. В ЕСР смена направления должна быть согласована:

хост запрашивает реверс установкой ReverseRequest#, после чего он должен

дождаться подтверждения сигналом AckReverse#. Поскольку предыдущий цикл

мог выполняться по прямому доступу, драйвер должен дождаться завершения

прямого доступа или прервать его, выгрузить буфер

FIFO, определив точное значение счетчика переданных байт, и только после

этого запрашивать реверс.

Обратная передача данных состоит из следующих шагов:

- Хост запрашивает изменение направления канала, устанавливая низкий уровень на линии ReverseRequest#.

- ПУ разрешает смену направления установкой низкого уровня на линии AckReverse#.

- ПУ помещает данные на шину канала и устанавливает признак цикла данных (высокий уровень) или команды (низкий уровень) на линии PeriphAck.

- ПУ устанавливает низкий уровень на линии PeriphClk, указывая на действительность данных.

- Хост отвечает установкой высокого уровня на линии HostAck.

- ПУ устанавливает высокий уровень линии PeriphClk; этот перепад может использоваться для фиксации данных хостом.

- Хост устанавливает низкий уровень на линии HostAck для указания на готовность к приему следующего байта.

Режимы и регистры ЕСР-порта

Программный интерфейс и регистры ЕСР для адаптеров IEEE 1284 определяет спецификация Microsoft. Определены режимы (табл. 9), в которых может функционировать адаптер. Они задаются полем Mode регистра ECR (биты [7:5]).

Регистровая модель адаптера ЕСР (табл. 10) использует свойства архитектуры стандартной шины и адаптеров ISA - для дешифрации адресов портов ввода/вывода задействуются только 10 младших линий шины адреса. Поэтому, например, обращения по адресам Port, Port+400h, Port+800h... будут восприниматься как обращения к адресу Port, лежащему в диапазоне 0-3 FFh. Современные PC и адаптеры декодируют большее количество адресных бит, поэтому обращения по адресам 0378h и 0778h будет адресованы двум различным регистрам. Помещение дополнительных регистров ЕСР "за спину" регистров стандартного порта (смещение 400-402h) преследует две цели. Во-первых, эти адреса никогда не использовались традиционными адаптерами и их драйверами, и их применение в ЕСР не приведет к сужению доступного адресного пространства ввода/вывода. Во-вторых, этим обеспечивается совместимость со старыми адаптерами на уровне режимов 000-001 и возможность определения присутствия EСР-адаптера через попытку обращения к его расширенным регистрам.

Таб.9.

Режимы ECP-порта

|

Режим

|

Название

|

Описание

|

|

000

|

SPPmode

|

Стандартный (традиционный) режим |

|

001

|

Bi-directional mode

|

Двунаправленный порт (тип 1 для PS/2) |

|

010

|

Fast Centronics

|

Однонаправленный с использованием FIFO и DMA |

|

011

|

ECP Parallel Port

mode

|

ECP |

|

100

|

EPP Parallel Port

mode* |

Перевод в режим EPP |

|

101

|

Зарезервировано

|

- |

|

110

|

Test mode

|

Тестирование работы FIFO и прерываний |

|

111

|

Configuration mode

|

Доступ к конфигурационным регистрам |

* Этот режим не входит в спецификацию Microsoft, но трактуется как EPP контроллером SMC FDC37C665/666 и многими другими.

Каждому режиму ECP соответствуют (и доступны) свои функциональные регистры. Переключение режимов осуществляется записью в регистр ECR. "Дежурными" режимами, включаемыми по умолчанию, являются 000 или 001. В любом из них работает полубайтный режим ввода. Из этих режимов всегда можно переключиться в любой другой, но из старших режимов (010-111) переключение возможно только в 000 или 001. Для корректной работы интерфейса перед выходом из старших режимов необходимо дождаться завершения обмена по прямому доступу и очистки FIFO-буфера.

В режиме 000 (SPP) порт работает как стандартный однонаправленный программно-управляемый SPP.

В режиме 001 (Bi-Di PS/2) порт работает как двунаправленный порт PS/2 типа 1. От режима 000 отличается возможностью реверса канала данных по биту CR.5.

Режим 010(Fast Centronics) предназначен только для высокопроизводительного вывода через FIFO-буфер с использованием DMA. Сигналы квитирования по протоколу Ceritromcs вырабатываются аппаратно. Сигнал запроса прерывания вырабатывается по состоянию FIFO-буфера, но не по сигналу Аск# (запрос одиночного байта "не интересует" драйвер быстрого блочного вывода).

Режим 011 является собственно режимом ЕСР, описанным ранее. Поток данных и команд, передаваемых в ПУ, помещается в FIFO-буфер через регистры ECPDFIFO и ECPAFIFO соответственно. Из FIFO они выводятся с соответствующим признаком цикла (состояние линии HostAck). Принимаемый поток данных от ПУ извлекается из FIFO-буфера через регистр ECPDFIFO. Получение адреса в командном цикле от ПУ не предусматривается. Обмен с регистром ECPDFIFO может производиться и по каналу DMA.

Компрессия по методу RLE при передаче выполняется программно. Для передачи подряд более двух одинаковых байт данных в регистр ECPAFIFO записывается байт, у которого младшие 7 бит содержат счетчик RLC (значение RLC=127 соответствует 128 повторам), а старший бит нулевой. После этого в ECPDFIFO записывается сам байт. Отсюда очевидно, что вывод данных с одновременным использованием компрессии и DMA невозможен. Принимая эту пару байт (командный байт и байт данных), ПУ осуществляет декомпрессию. При приеме потока от ПУ адаптер ЕСР декомпрессию осуществляет аппаратно и в FIFO-буфер помещает уже декомпрессированные данные.

Режим 100 (ЕРР) - один из способов включения режима ЕРР.

Режим 110 (Test Mode) предназначен для тестирования взаимодействия FIFO и прерываний. Данные могут передаваться в/из регистра TFIFO с помощью DMA или программным способом. На внешний интерфейс обмен не воздействует. Адаптер отрабатывает операции вхолостую на максимальной скорости интерфейса (как будто сигналы квитирования приходят без задержек). Адаптер следит за состоянием буфера и по мере необходимости вырабатывает сигналы запроса прерывания. Таким образом программа может определить максимальную пропускную способность канала.

Режим 111 (Configuration mode) предназначен для доступа к конфигурационным регистрам. Вьвделение режима защищает адаптер и протокол от некорректных изменений конфигурации в процессе обмена.

Таб.

10.

|

Смещение

|

Имя

|

R/W

|

Режимы

ЕСР*

|

Название

|

|

000

|

DR

|

R/W

|

000-001

|

Data Register |

|

000

|

ECPAF1FO

|

R/W

|

011

|

ЕСР Address FIFO |

|

001

|

SR

|

R/W

|

Все

|

Status Register |

|

002

|

CR

|

R/W

|

Все

|

Control Register |

|

400

|

SDFIFO

|

R/W

|

010

|

Parallel Pwt Data FIFO |

|

400

|

ECPDFIFO

|

R/W

|

011

|

ЕСР Data FIFO |

|

400

|

TFIFO

|

R/W

|

110

|

Test FIFO |

|

400

|

CNFGA

|

R

|

111

|

Configuration Register A |

|

401

|

CNFGB

|

R/W

|

111

|

Configuration Register В |

|

402

|

ECR

|

R/W

|

Все

|

Extended Control Register |

* Регистры доступны только в указанных режимах (режим задается битами 7-5 регистра ECR).

Регистр данных DR используется для передачи данных только в программно-управляемых режимах (000 и 001).

Регистр состояния SR передает значение сигналов на соответствующих линиях (как в SPP).

Регистр управления CR имеет назначение бит, совпадающее с SPP. В режимах 010, 011 запись в биты 0, 1 (сигналы AutoLFft и Strobe*) игнорируется.

Регистр ECPAF1FO служит для помещения информации командных циклов (канального адреса или счетчика RLE, в зависимости от бита 7) в FIFO-буфер. Из буфера информация будет выдана в командном цикле вывода.

Регистр SDFIFO используется для передачи данных в режиме 010. Данные, записанные в регистр (или посланные по каналу DMA), передаются через буфер FIFO по реализованному аппаратно протоколу Centronics. При этом должно быть задано прямое направление передачи (бит CR.5=0).

Регистр DFIFO используется для обмена данными в режиме 011 (ЕСР). Данные, записанные в регистр или считанные из него (или переданные по каналу DMA), передаются через буфер FIFO по протоколу ЕСР.

Регистр TFIFO обеспечивает механизм тестирования FIFO - буфера в режиме 110.

Регистр ECPCFGA позволяет считывать информацию об адаптере (идентификационный код в битах [7:4].

Регистр ECPCFGB хранит информацию, необходимую драйверу. Запись в регистр не влияет на работу порта.

Регистр ECR - главный управляющий регистр ЕСР.

Назначение бит регистра ECR

ECR[7:5] - ЕСР MODE - задает режим ЕСР.

ECR.4 - ERRINTREN^t (Error Interrupt Disable) - запрещает прерывания по сигналу Еггог# (при нулевом значении бита по отрицательному перепаду на этой линии вырабатывается запрос прерывания).

ECR.3 - DMAEN (DMA Enable) - разрешает обмен по каналу DMA.

ECR.2 - SERVICEINTR (Service Interrupt) - запрещает сервисные прерывания, которые вырабатываются по окончании цикла DMA (если он разрешен), по порогу заполнения/опустошения FIFO-буфера (если не используется DMA) и по ошибке переполнения буфера сверху или снизу.

ECR. 1 - FIFOFS (FIFO Full Status) - сигнализирует о заполнении буфера; при FIFOFS=1 в буфере нет ни одного свободного байта.

ECR. О - FIFOES (FIFO Empty Status) - указывает на полное опустошение буфера; комбинация FIFOFS=FIFOES=I означает ошибку работы с FIFO (переполнение сверху или снизу).

Когда порт находится в стандартном или двунаправленном режимах (000 или 001), первые три регистра полностью совпадают с регистрами стандартного порта. Так обеспечивается совместимость драйвера со старыми адаптерами и старых драйверов с новыми адаптерами.

По интерфейсу с программой FCP-порт напоминает ЕРР: после установки режима (записи кода в регистр ECR) обмен данными с устройством сводится к чтению или записи в соответствующие регистры. За состоянием FIFO-буфера наблюдают либо по регистру ECR, либо по обслуживанию сервисных прерываний от порта. Весь протокол квитирования генерируется адаптером аппаратно. Обмен данными с ЕСР - портом (кроме явного программного) возможен и по прямому доступу к памяти (каналу DMA), что эффективно при передаче больших блоков данных.